演算回路(2)ALU・レジスタ

現在、CSの勉強のために、コンピュータアーキテクチャ (電子情報通信レクチャーシリーズ)を読んでいる。

P.13

コンピューターの演算サイクルをなんとなく理解できたが、この基礎をしっかり抑えておきたいと思い、自分なりにまとめてみた。

ALU(Arithmetic Logic Unit)

ALU(Arithmetic Logic Unit)は、算術論理演算装置と呼ばれ、制御信号によって様々な演算を行うことができる組み合わせ回路である。

- 算術演算:加算・減算・乗算・除算など

- 論理演算:AND・OR・NOT・XORなど

74181

Texas Instrumentsの74シリーズであるSN74181は、4ビットの加算・減算・AND・ORなど32種類の演算を1つのパッケージで実現することができる。(乗算除算は、加減算に比べ複雑な回路が必要なため、74シリーズの中には乗除算機能はない。)

データシートより、論理回路は以下のようになっている。(ACTIVE HIGH(正論理)の場合のみを引用している。すなわち、H=1, L=0である。)

- 制御信号:S0 - S3

- M = 1の場合、論理演算

- M = 0の場合、算術演算

- データ入力:A0 - A3, B0 - B3

- データ出力:F0 - F3

- Cn:桁上げ入力

- Co:桁上げ出力

- A=B:データ入力が等しい場合、1になる

- CG, CP:桁上げ先見出力(ルックアヘッドキャリー方式)

論理回路図より、各桁に桁上げを計算する回路があり、桁上げに関してルックアヘッドキャリー方式を採用していることがわかる。

レジスタ

レジスタは、フリップフロップを並列に並べた(一時的な)記憶装置である。

フリップフロップ

フリップフロップ(Flip Flop)は、1ビットの記憶装置である。すなわち、"0"または"1"の状態として保持することができる論理回路。FFには主に4つの種類がある。

- RS-FF:Reset-Set型。FFの基本回路。

- JK-FF:RS-FFの(1,1)入力で反転するように改善。

- D-FF:Delay型。同期型において、入力値が最大1クロック遅れて出力される。

- T-FF:Toggle型。入力がHになると、出力が反転する。

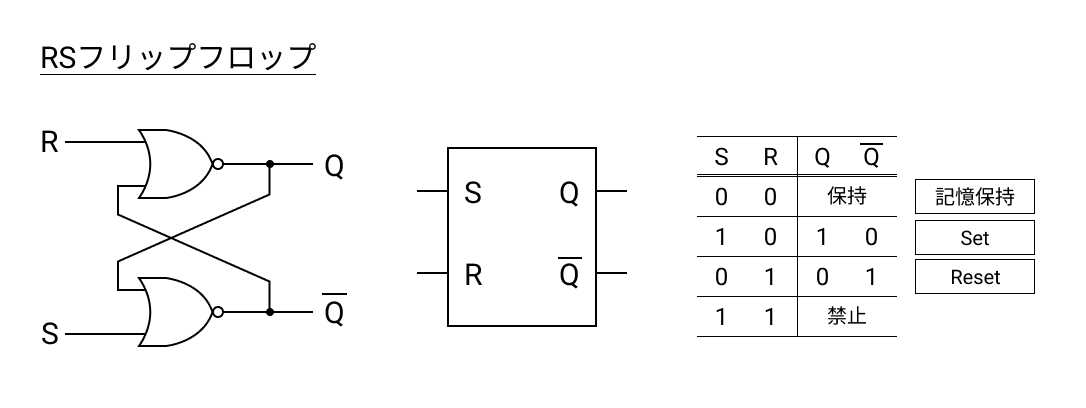

RS-FF

RS-FFは、SET/RESETの2つの入力端子があり、SETにHIGHが入力されると、RESETにHIGHが入力されるまで出力の状態を保持し続ける。回路図は、2つのNOR素子で構成される。

(注意)SET/RESETの2つの入力端子に、両方HIGHが入力されることは禁止されている。

(注意)SET/RESETの2つの入力端子に、両方HIGHが入力されることは禁止されている。

JK-FF

JK-FFは、RS-FFで禁止されているSET/RESETの2つの入力端子にHIGHが入力された場合、現在保持している値を反転する。

T-FF

T-FFは、入力TがHIGHになるたびに出力が反転する。TはToggleの略である。

D-FF

D-FFは、入力DにHIGHが入力されるとHIGHを保持してHIGHを出力する。反対に、入力DにLOWが入力されるとLOWを保持してLOWを出力する。RS-FFの入力が(0,0)になる条件がないため、D-FFの出力は現在保持している状態に依存せず、必ず入力だけから決定される。

また、エッジトリガ型の同期タイプの場合、Dの値が変わっても、次のCLKの立ち上がりエッジまでは出力が切り替わらず保持される。

nビットレジスタ

- データ長がnビットの場合、n個のフリップフロップで構成する

- 入力:クロック(CLK)に同期して読み込まれる

- パラレル(並行)入力

- シリアル(直列)入力

- 出力:記憶したデータは出力端子から読み出される

- パラレル(並行)出力

- シリアル(直列)出力

- シリアルでの入出力が可能なレジスタは、シフトレジスタと言われる。

- パラレル⇆シリアル変換に使用される

- 書き込み許可:WE(Write Enable)

- 0=現在の値を保持

- 1=書き込み

- 出力許可:OE(Output Enable)

- 0=高インピーダンス状態(電流が流れない状態)にして、出力信号を遮断する

- 1=出力

- 初期化:CLEAR

入力端子から、順に (0, 1, 0, 0)と入力されたシリアル通信を 4ビットの信号として、(PO3,PO2,PO1,PO0)でパラレル通信として取り出すことができている。

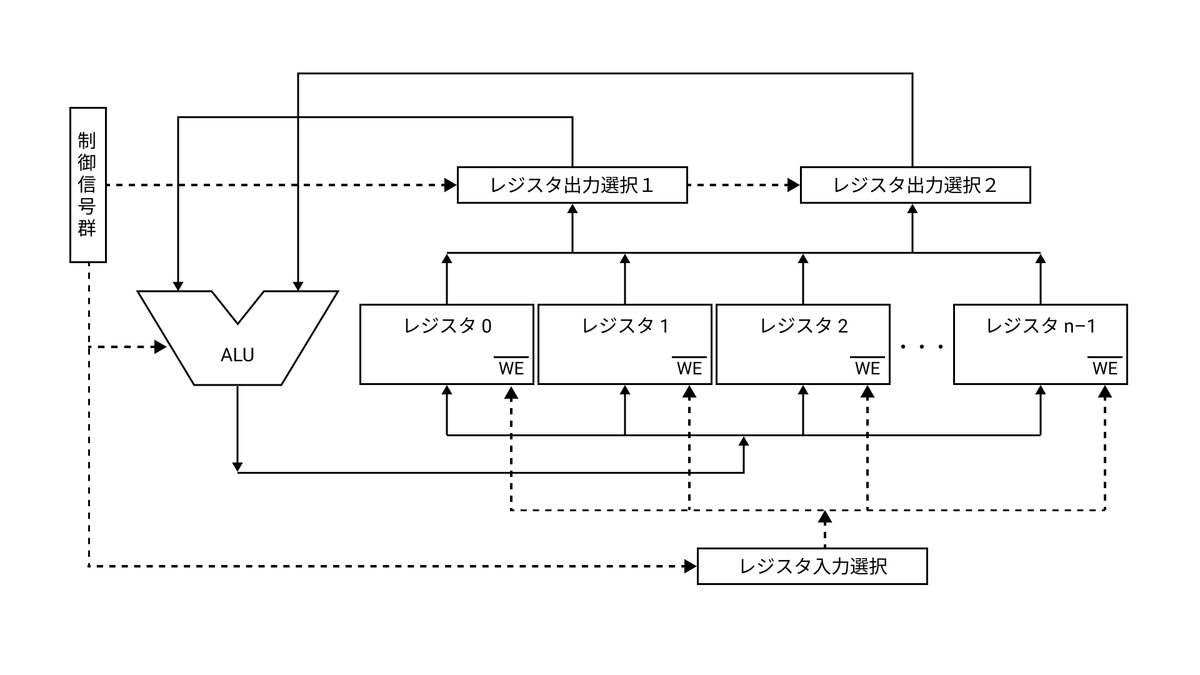

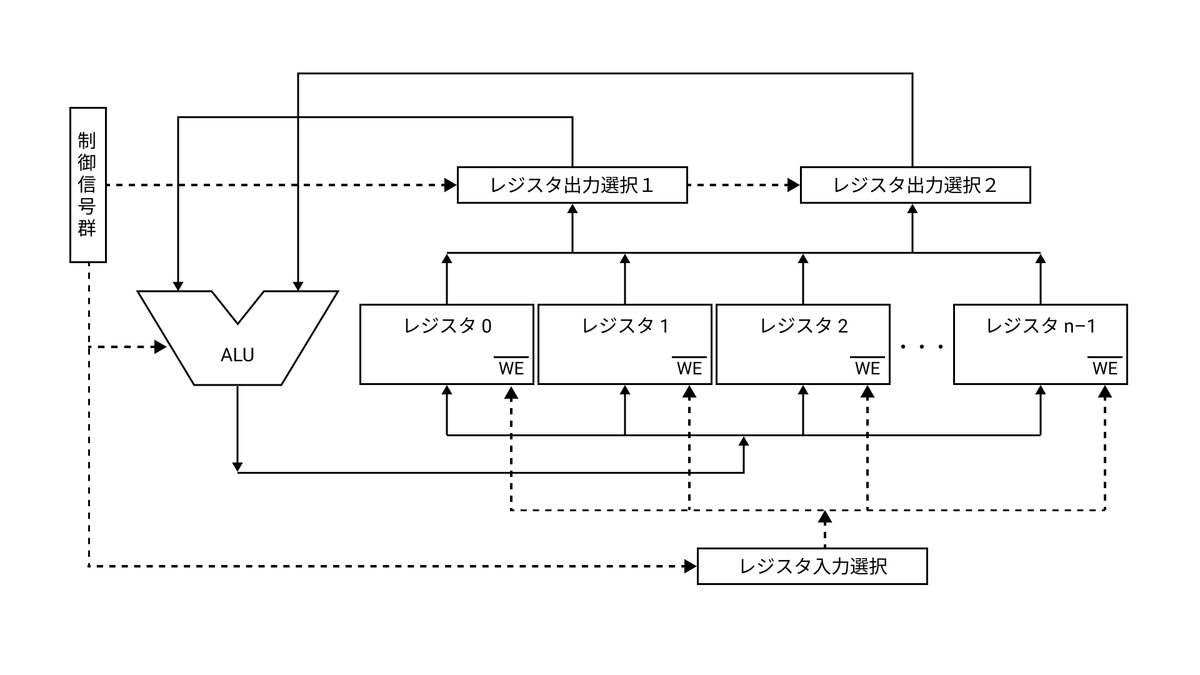

ALUとレジスタの結合

コンピュータは、レジスタに蓄えられたデータを取り出し、これを入力としてALUで演算を行い、再度結果をレジスタに格納する、というサイクルを繰り返すことで計算を行う。

これまでに見てきた知識を総動員することで、上図の概念図を理解することができる。

- 制御信号群が任意のレジスタから必要なデータを取り出す。(レジスタ出力選択1, レジスタ出力選択2)

- 制御信号群がALUの演算方式を決定し、(1)の取り出したデータをALUの入力とし、演算を行う

- 制御信号群が(2)で行った演算結果の出力を任意のレジスタに格納させる(レジスタ入力選択)

上記からわかるように、演算装置であるALUと一時記憶装置であるレジスタをきちんと制御する制御信号群がとても重要であることがわかる。

この制御信号群こそが、コンピュータアーキテクチャを考える上で最も大切なことである。

まとめ

ALUやレジスタに関して、理解を深めることができた。そして、コンピューターの計算の基本的な流れを掴めたことで、ALUとレジスタを制御して特定の機能を実現している制御信号群という存在の大きさを知ることができた。

次からは、この制御信号群が何者か、理解を深めていきたい。